- 您现在的位置:买卖IC网 > Sheet目录2000 > IDTCV115-2PVG (IDT, Integrated Device Technology Inc)IC FLEXPC CLK PROGR P4 56-TSSOP

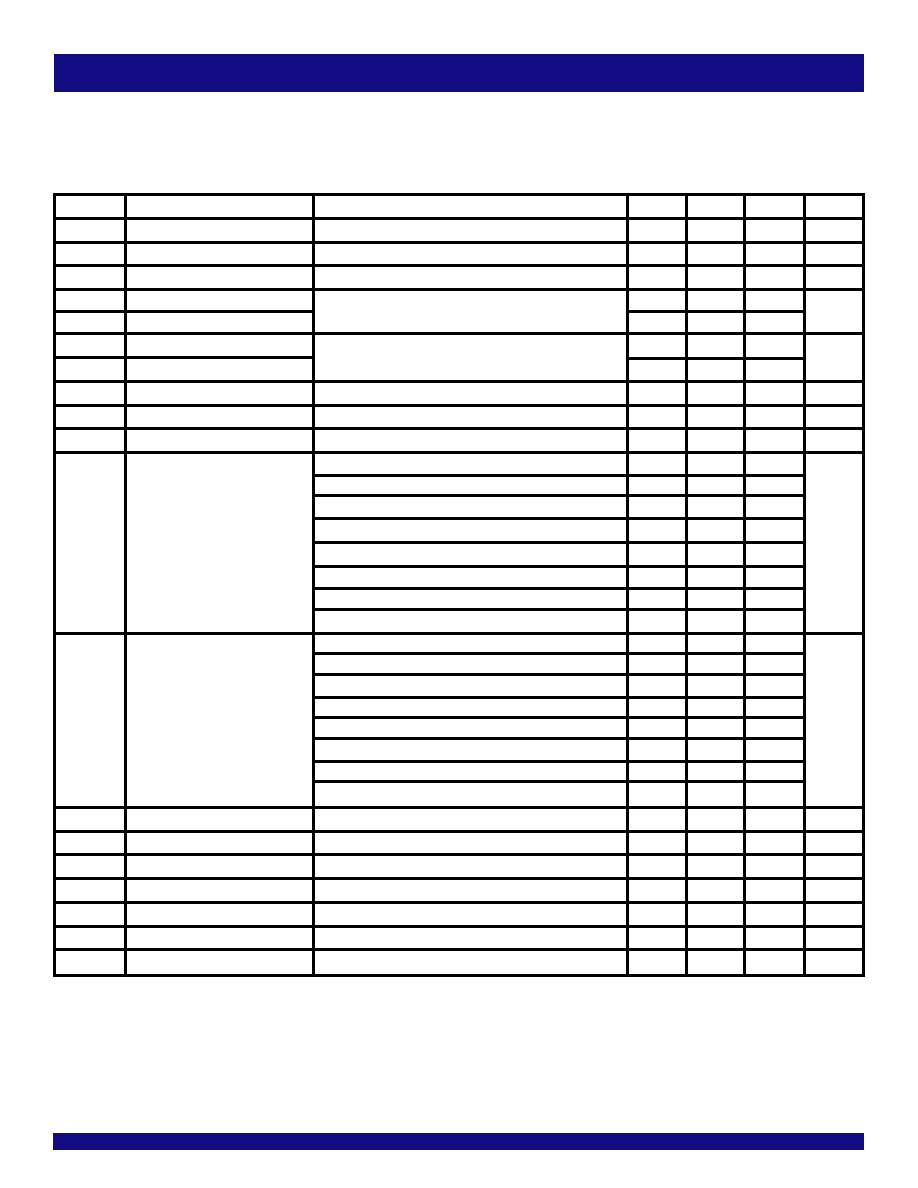

COMMERCIALTEMPERATURERANGE

14

IDTCV115-2

PROGRAMMABLEFLEXPCCLOCKFORP4PROCESSOR

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

ZO

Current Source Output Impedance(2) VO = VX

3000

—

Ω

VOH3

Output HIGH Voltage

IOH = -1mA

2.4

—

V

VOL3

Output LOW Voltage

IOL = 1mA

—

0.4

V

VHIGH

Voltage HIGH(2)

Statistical measurement on single-ended signal using

660

—

850

mV

VLOW

Voltage LOW(2)

oscilloscope math function

–150

—

150

VOVS

Max Voltage(2)

Measurement on single-ended signal using absolute value

—

1150

mV

VUDS

Min Voltage(2)

–300

—

VCROSS(ABS)

Crossing Voltage (abs)(2)

250

—

550

mV

d - VCROSS

Crossing Voltage (var)(2)

Variation of crossing over all edges

—

140

mV

ppm

Long Accuracy(2,3)

See TPERIOD Min. - Max. values

–300

—

300

ppm

400MHz nominal/spread

2.4993

—

2.5008

333.33MHz nominal/spread

2.9991

—

3.0009

266.66MHz nominal/spread

3.7489

—

3.7511

TPERIOD

Average Period(3)

200MHz nominal/spread

4.9985

—

5.0015

ns

166.66MHz nominal/spread

5.9982

—

6.0018

133.33MHz nominal/spread

7.4978

—

7.5023

100MHz nominal/spread

9.997

—

10.003

96MHz nominal

10.4135

—

10.4198

400MHz nominal/spread

2.4143

—

333.33MHz nominal/spread

2.9141

—

266.66MHz nominal/spread

3.6639

—

200MHz nominal/spread

4.9135

—

TABSMIN

Absolute Min Period(2,3)

166.66MHz nominal/spread

5.9132

—

ns

133.33MHz nominal/spread

7.4128

—

100MHz nominal/spread

9.912

—

96MHz nominal

10.1635

—

tR

Rise Time(2)

VOL = 0.175V, VOH = 0.525V

175

—

700

ps

tF

Fall Time(2)

VOL = 0.175V, VOH = 0.525V

175

—

700

ps

d-tR

Rise Time Variation(2)

—

125

ps

d-tF

Fall Time Variation(2)

—

125

ps

dT3

Duty Cycle(2)

Measurement from differential waveform

45

—

55

%

tSK3

Skew(2)

VT = 50%

—

100

ps

tJCYC-CYC

Jitter, Cycle to Cycle(2)

Measurement from differential waveform

—

85

ps

ELECTRICAL CHARACTERISTICS - CPU, SRC, AND DOT96 0.7 CURRENT MODE

DIFFERENTIAL PAIR(1)

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = 0°C to +70°C, Supply Voltage: VDD = 3.3V ± 5%; CL = 2pF

NOTES:

1.

SRC clock outputs run only at 100MHz or 200MHz. Specs for 133.33 and 166.66 do not apply to SRC clock pair.

2.

This parameter is guaranteed by design, but not 100% production tested.

3.

All long term accuracy and clock period specifications are guaranteed with the assumption that the REF output is at 14.31818MHz.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDTCV115FPVG

IC FLEXPC CLK PROGR P4 56-SSOP

IDTCV119EPVG8

IC CLK GEN DESKTOP PC 48-SSOP

IDTCV133PAG

IC FLEXPC CLK PROGR P4 56-TSSOP

IDTCV136PAG

IC FLEXPC CLK ATI RS400 56-TSSOP

IDTCV137PAG

IC FLEXPC CLK AMD K8 56-TSSOP

IDTCV142PAG

IC FLEXPC CLK PROGR P4 56-TSSOP

IDTCV146PVG

IC FLEXPC CLK PROGR P4 56-SSOP

IDTCV149PAG

IC FLEXPC CLK PROGR K8 56-TSSOP

相关代理商/技术参数

IDTCV115-2PVG8

功能描述:IC FLEXPC CLK PROGR P4 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV115-4PVG

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV115-4PVG8

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV115C

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:PROGRAMMABLE FLEXPC CLOCK FOR P4 PROCESSOR

IDTCV115CPV

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:PROGRAMMABLE FLEXPC CLOCK FOR P4 PROCESSOR

IDTCV115CPVG

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV115CPVG8

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV115FPVG

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT